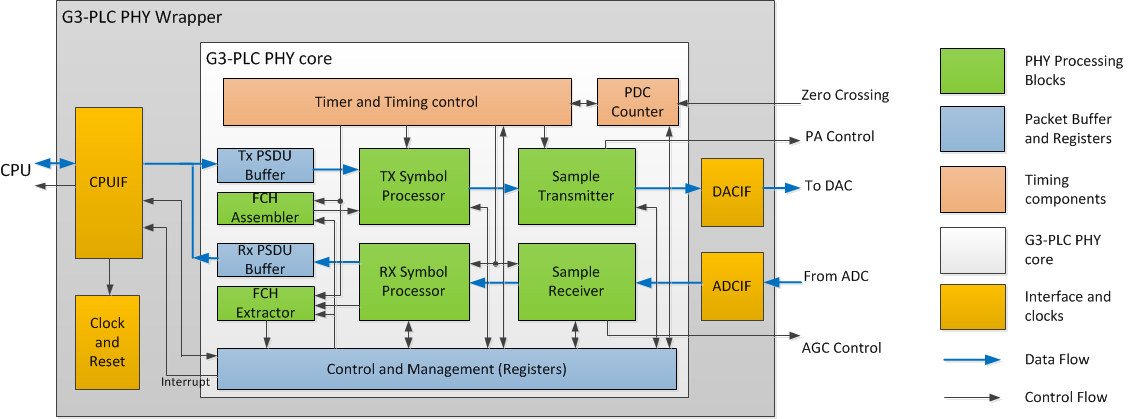

G3-PLC物理层算法的FPGA实现

与欧洲瑞士一个合作企业共同完成了G3-PLC的协议栈开发,我公司主要负责硬件试验系统搭建、物理层算法设计、物理层的FPGA实现等任务。该案例中我公司使用了多个公司自主创新的接收机算法,实现了性能与资源的最优匹配。

FPGA实现结构图:

逻辑资源使用情况

Modules | Equivalent Gates | Memory(bits) |

TX Symbol Processor | 27,512 | 45,128 |

RX Symbol Processor | 105,352 | 182,208 |

Sample Transmitter | 24,856 | 20,480 |

Sample Receiver | 82,776 | 144,384 |

PSDU Buffer | 72 | 4,096 |

Timing Blocks | 3,320 | 0 |

Configuration and Management | 21,496 | 0 |

Others | 13,064 | 20,000 |

Total | 278,448 | 396,296 |

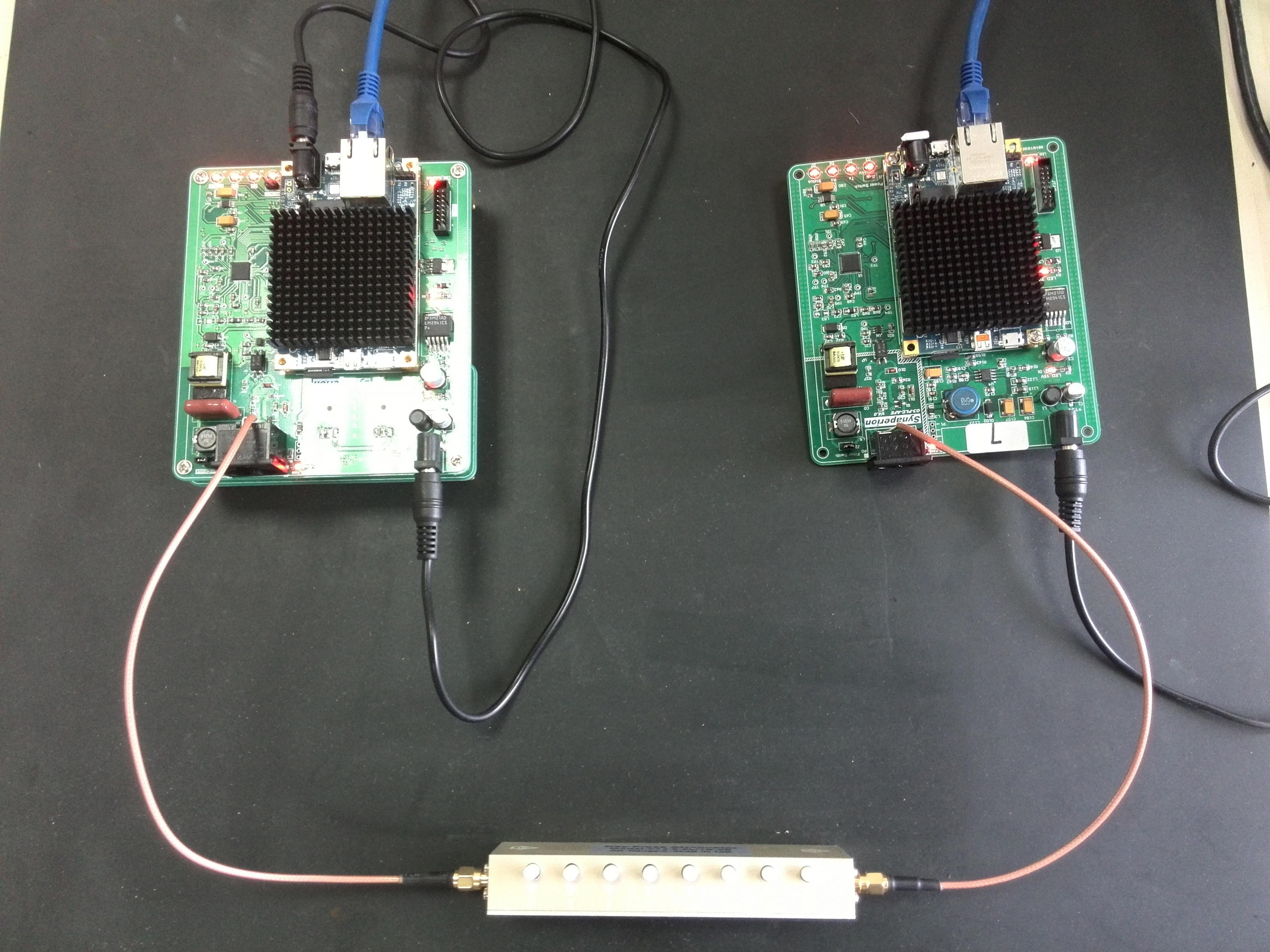

调试实景展示

(公司内部调试)

(客户方调试)

2018年5月14日 08:48

ꄘ浏览量:0